KOD ÇÖZÜCÜLERİN VE ANAHTARLAYICILARIN VHDL İLE TASARIMI

KOD ÇÖZÜCÜLERİN VE ANAHTARLAYICILARIN VHDL İLE TASARIM VE BENZETİMİ

A. VHDL Mntık Vektörleri (Logic Arrays): hatırlayacağınız üzere, tek bitlik mantık için STD_LOGIC en fazla kullanılan veri tiplerinden biridir. Çok bitli mantık değişkenlerinin temsili için ise STD_LOGIC_VECTOR veri tipini şu şekilde kullanıyoruz:

X: in STD_LOGIC_VECTOR((N-1) downto 0); N-bit giriş değişkeni X, en soldaki bir en etkin olanıdır.

Y: out STD_LOGIC_VECTOR((N-1) downto 0); N-bit çıkış değişkeni Y, en soldaki bir en etkin olanıdır.

Z: in STD_LOGIC_VECTOR(0 to (N-1)); N-bit giriş değişkeni Z, en sağdaki bir en etkin olanıdır.

Y: out STD_LOGIC_VECTOR(0 to (N-1)); N-bit çıkış değişkeni Y, en sağdaki bir en etkin olanıdır.

VHDL programlamada begin ve end işaretleri arasındaki tüm cümleler aynı anda paralel olarak işlenirler. Cümlelerin sırası VHDL kodunun çıkışlarını etkilemez.

B. Seçenekli Sinyal Değerlemeleri:

Seçenekli sinyaller için değer atamalarına yönelik genel format şu şekildedir:

with Seçenekli_İfade select

sinyal_ismi <= atanmış_sinyal when seçenekler

{, atanmış_sinyal when seçenekler}; — ek değerlemeler

İstenilen sayıda seçenekli sinyaller ve karşılık gelen when seçimleri eklenebilir. Eğer birden çok alternatif arasından seçim yapmak gerekiyor ise:

seçenek {| seçenek}

formatı kullanılır. Burada seçenekler arasındaki dikey çizgi verieln seçeneklerden herhangi birinin “Seçenekli_İfade” ile eşleştirilebileceği anlamını taşır. Herbir seçenek, bir ifadeyi, bir aralığı (ileriye veya geriye doğru sıralanmış), veya others anahtar kelimesini belirtir..

Seçim ifadesi işlendikten sonra verilen seçeneklerle karşılaştırılır ve bir eşleştirme olması halinde eşlenen ifadeye, aksi halde others seçeneğine eşitlenir. others seçeneği daha önce kullanılmayan herhengi bir değerin atanması anlamına gelir. Her durumda, seçilen ifade (değer) atama operatörünün (<=) sol tafarında yer alan iafdeye atanır.

Örnek:

with Sel select

Y <= A when “00”,

B when “01”,

C when “10”,

D when others;

Örnek:

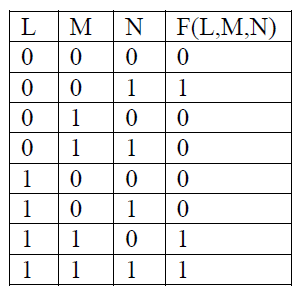

Aşağıdaki doğruluk tablosunda verilen işlevi gerçeklemek için gereken VHDL kodunu yazınız. Sadece seçenekli sinyal değerleme cümlelerini kullanınız.

architecture Islev of Benim_Devrem is

begin

with ( (L = ‟0‟ AND M = ‟0‟ and N = ‟1‟) or

(L = ‟1‟ AND M = ‟1‟) ) select

F3 <= „1‟ when „1‟,

„0‟ when „0‟,

„0‟ when others;

end Islev;

C. Şartlı (Kısıtlamalı) Sinyal Değerleme:

Kısıtlamalı sinyal değerlendirmeleri için genel format aşağıdaki gibidir:

[isim:]

sinyal_ismi <= seçilen_sinyal when kısıtlama else

{,seçilen_sinyal when kısıtlama else}; — ek kısıtlamalar

seçilen_sinyal;

İstenildiği kadar “seçilen_sinyal” ve when durumu kullanılabilir, when durumları sırasıyla kontrol edilerek doğru (TRUE) olan bulununcaya kadar devam edilir; yada ensondaki else‟i takip eden “seçilen_sinyal” sinyal_ismine eşitlenir.

Örnek:

Y <= A when Sel = “00” else

B when Sel = “01” else

C when Sel = “10” else

D when others;

veya

Y <= A when Sel = “00” else

B when Sel = “01” else

C when Sel = “10” else

„0‟;

Örnek:

Bir öncelik kodlayıcısının (priority encoder) kısıtlamalı değerleme cümleleri kullanılarak kurulan VHDL kodu şu şekilde yazılabilir:

library IEEE

use IEEE.std_logic_1164.all;

entity oncelik_kodlayıcı is

port (D: in std_logic_vector (4 downto 0);

A: out std_logic_vector (2 downto 0);

V: out std_logic);

end oncelik_kodlayıcı;

architecture veri_akisi of oncelik_kodlayıcı is

begin

A <= “100” when D(4) = ‘1’

else “011” when D(4 downto 3) = “01”

else “010” when D(4 downto 2) = “001”

else “001” when D(4 downto 1) = “0001”

else “000” when D = “00001”

else “XXX”;

V <= not(D = “00000”);

end veri_akisi;

D. Bileşimsel “processes”‟ler: Bileşimsel mantığı gerçeklemede yaygın olarak kullanılan diğer bir VHDL cümlesi de process dir. Bir process cümlesi VHDL programının genelinde ilgili yapının diğer cümleleriyle paralel olarak işlenir, fakat process alanı içinde yeralan cümleler ise seri olarak işlenir.

process cümlelerinin çıkış sinyalleri bü cümlelerin giriş sinyallerinin (duyarlılık listesi olarak da adlandırılırlar) cinsinden ifade edilir. Bir process cümlesi yapısı içnde yeralan tüm sinyalleri duyarlılık listesinde bulundurmak zorundadır.

Bileşimsel process cümlelerinin genel formatı şu şekildedir:

[process_adı:]

process (duyarlılık_listesi)

[process tanımlamaları;]

begin

[ardışık (seri) cümleler;]

end process [pocess_adı];

process yapısı içinde yeralan VHDL cümleleri seri (ardışık) işlenir ve bir cümlenin işlenmesine process duyarlılık listesindeki sinyallerin bir veya daha fazlasında bir değişiklik olduğu anda hemen başlanır. process yapısındaki sinyallerin işlenmesi process sonuna ulaşılıncaya kadar devam eder.

process yapılarında yaygın olarak kullanılan iki ardışık VHDL cümlesi IF ve CASE cümleleridir. Bu iki cümlenin işlevleri ve yapıları birbirinin aynıdır.

IF Cümlesi

if cümlesi seri cümlelerin işlenmesinde koşullu dallanmayı olanaklı kılar. If cümlesinde kullanılan koşulların alacağı değerlere göre, veri ve işlem akışı bir dala, veya hiçbir yöne, doğru yöneltilir. If cümlesinin genel formatı şöyledir:

if (koşul) then

{ ardışık cümleler }

elsif (koşul) then

{ ardışık cümleler }

else

{ ardışık cümleler }

end if;

Burada dikkat edilecek nokta şudur: VHDL if cümlesi ile VHDL kısıtlamalı sinyal değerleme cümleleri eşdeğerdirler; tek fark if cümlesinin seri, kısıtlamalı değerleme cümlelerinin ise paralel işlenmesidir..

Örnek:

8×1 MUX ünitesini gerçekleyen bir VHDL kodu aşağıda verilmiştir. Bu kod içerisinde if cümlelerinin nasıl kullanıldığına dikkat ediniz.

entity mux_8t1 is

port ( Data_in : in std_logic_vector (7 downto 0);

SEL : in std_logic_vector (2 downto 0);

F_CTRL : out std_logic);

end mux_8t1;

architecture my_8t1_mux of mux_8t1 is

begin

my_proc: process (Data_in,SEL)

begin

if (SEL = “111”) then F_CTRL <= Data_in(7);

elsif (SEL = “110”) then F_CTRL <= Data_in(6);

elsif (SEL = “101”) then F_CTRL <= Data_in(5);

elsif (SEL = “100”) then F_CTRL <= Data_in(4);

elsif (SEL = “011”) then F_CTRL <= Data_in(3);

elsif (SEL = “010”) then F_CTRL <= Data_in(2);

elsif (SEL = “001”) then F_CTRL <= Data_in(1);

elsif (SEL = “000”) then F_CTRL <= Data_in(0);

else F_CTRL <= „0‟;

end if;

end process my_proc;

end my_8t1_mux;

Case Cümlesi

case cümlesi işlevi bakımından if cümlesi ne benzerdir. case cümlesi nin temel farklılığı işlem yönünün ilgili ifade değerinin sadece doğru (TRUE) olarak bulunması durumunda belirlenmesidir. case cümlesinin her işlenişinde yapısı içinde yeralan seri cümlelerden sadece bir tanesi seçilerek işlenir ve bu cümle ilk when koşulunun doğrulandığı noktada belirlenir. case cümlesinin genel formatı şu şekildedir:

case (ifade) is

when seçenekler =>

{seri cümleler}

when seçenekler =>

{seri cümleler}

when others =>

{seri cümleler}

end case;

VHDL case cümlesi ile VHDL kısıtlamalı değerleme cümlesi işlev bakımından eşdeğerdir, farkları case cümlesinin bir process yapısı içnde seri olarak işlenmesidir.

Örnek:

Bir 2×4 DEC için VHDL kod aşağıda verilmiştir.

library ieee;

use ieee.std_logic_1164.all;

entity DECODER is

port( I: in std_logic_vector(1 downto 0);

O: out std_logic_vector(3 downto 0));

end DECODER;

architecture behavior of DECODER is

begin

process (I)

begin

case I is

when “00” => O <= “0001”;

when “01” => O <= “0010”;

when “10” => O <= “0100”;

when “11” => O <= “1000”;

when others => O <= “XXXX”;

end case;

end process;

end behavior;

Son yorumlar